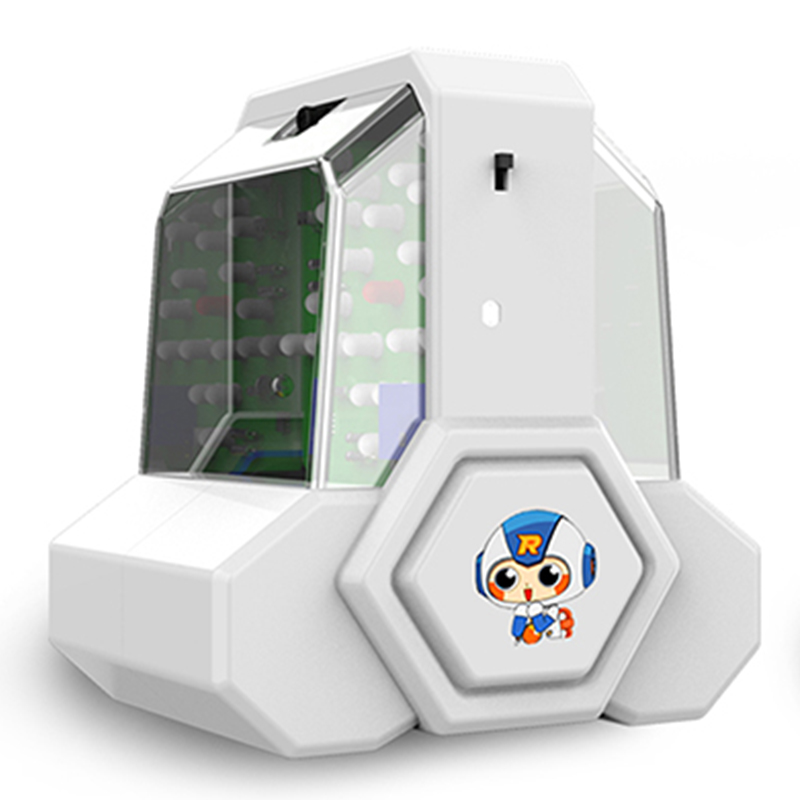

公司:重慶環潔智創新科技有限公司

主營:產品研發設計、模具加工生產

手機:15978927637

地址:重慶茶園經開區美林路16號昌龍國際A9棟5樓

如何進行PCB設計的時鐘信號的布局和走線?

大家好,今天小編來為大家解答以下的問題,關于如何進行PCB設計的時鐘信號的布局和走線?,pcb時鐘走線是否需要包地處理這個很多人還不知道,現在讓我們一起來看看吧!

如何從PCB層設計開始控制EMC問題

首先,EMI要從系統考慮,單憑PCB無法解決問題。疊層對EMI來說,主要是提供信號最短回流路徑、減小耦合面積和抑制差模干擾。另外地層與電源層緊密耦合,適當比電源層外延,對抑制共模干擾有好處。PCBEMC設計布局布線經驗1、整體布局1)高速、中速、低速電路要分開;2)強電流、高電壓、強輻射元器件遠離弱電流、低電壓、敏感元器件;3)模擬、數字、電源、保護電路要分開;4)多層板設計,有單獨的電源和地平面;5)對熱敏感的元器件(含液態介質電容、晶振)盡量遠離大功率元器件、散熱器等熱源。2、整體布線1)關鍵信號線走線避免跨分割;2)關鍵信號線走線避免“U”型或“O”型;3)關鍵信號線走線是否人為繞長;4)關鍵信號線是否距離邊沿和接口400mil以上;5)相同功能的總線要并行走,中間不要夾叉其它信號;6)晶振下面是否走線;7)開關電源下面是否走線;8)接收和發送信號要分開走,不能互相夾叉。

pcb時鐘走線是否需要包地處理

時鐘對整個電路來說是比較重要的一個信號,一般時鐘信號輸入阻抗很大,極容易受到干擾,屏蔽外界干擾就不得不考慮。和電視閉路線一個道理。

pcb時鐘通常用什么符號表示

一般用一個圓形表示。在圓形中央,一條垂直線代表整數小時,而外圓則被分成12等份,每份代表整數分鐘。有些時鐘符號也會標示秒,秒針則是在圓形中心一直不停地轉動。

總結數字電路設計的一般方法

我來自西北工業大學計算機學院微電子學研究所,現在是微電子學研究所的研一學生,專業方向是數字集成電路設計。在研一上學期,初步掌握了數字集成電路后端綜合設計方法,本篇學術素養課程報告主要討論在實現后端流程時的方法、經驗、以及相關的感悟。 一般而言,軟件工程師的需求量和硬件工程師的需求量是10:1,也就是說硬件工程師需求量遠小于軟件工程師,硬件工程師中又分為模擬和數字兩大類,模擬集成電路設計主要包括ADC、DAC、PLL等,數字集成電路設計則更偏向于實現特定功能的芯片,如CPU、GPU、MCU、MPU、DSP等。 事實上,發展到現階段,數字集成電路的設計方法已經在EDA工具的幫助之下十分類似于軟件開發了,典型的數字集成電路開發一般為以下步驟: 1、根據需求,自頂向下設計電路模塊,明確該數字系統需要實現什么功能,再具體細分到各個功能模塊。此時的設計圖形式一般為模塊框圖,使用visio或其他繪圖軟件實現。這個環節較為松散,但十分重要,因為根據需求設計大的模塊和指標時,必須要結合實際情況,否則到后期會經歷無限次返工甚至無法達到預定指標。一般由德高望重,經驗豐富的工程師進行總體設計。 2、定義好各個模塊之后,接下來就是具體實現各個模塊的功能。因為硬件描述語言的存在,我們可以很輕易的通過硬件描述語言來“寫”出模塊的實現方法,在本次實驗中,我使用的是VerilogHDL。具體代碼的復雜程度和模塊的復雜程度有關,我在這次實驗中采用的是“八位格雷碼計數器”電路設計。 3、完成“八位格雷碼計數器”的Verilog代碼后,需要對該設計進行“前仿真”。所謂前仿真,主要是為了驗證代碼是否描述正確,是否真正實現了所規劃的功能。一般使用modelsim軟件進行仿真,仿真成功進入下一階段,不成功則需要返回修改代碼。 4、前仿真成功后,已經有了功能正確的Verilog設計代碼,此時可以將代碼下載到FPGA板上進行驗證(Quartus,JTAG),驗證成功則證明此設計正確無誤。對于某些集成度要求不高且時間非常緊張的數字電路設計項目,可以直接使用FPGA來實現芯片功能。顯然,FPGA這種通用器件是不能滿足高集成、低功耗、專用性高ASIC設計需求的,只能用于較為簡單和粗獷的設計。 5、接下來進入后端流程。這時需要專用的服務器以及價格高昂的EDA工具支持。這也是為什么硬件設計入門較難的原因之一,如果一個沒有接觸過軟件編程的有志青年立志做軟件工程,一般一臺電腦,一本書就夠了,最多再買個正版編譯器(VS,Eclipse,DW等),但是要做硬件電路設計,一臺電腦一本書最多畫畫PCB。要做最核心的部分,必須使用功能強大的服務器和價格昂貴的EDA工具,因為普通的PC電腦負擔不起“后端綜合”的工作需求。而且大量linux下的復雜操作也會使人望而卻步。 6、準備好后端平臺后,就可以將“八位格雷碼計數器”放到平臺里,這時馬上需要考慮的問題是使用什么元件庫以及什么工藝?因為同樣一個與非門,不同元件庫有不同實現細節,MOS管細節可能都大相徑庭,另外還要考慮工藝,這些工藝的文件來自于相關廠家(TSMC,CSMS等),這也是個人無法做后端的原因之一——因為你幾乎不可能以自己的名義向臺積電商量工藝庫文件,畢竟作為一個涉世未深,無錢無術的初學者,你是無法充滿自信的和人數上萬、資金上億的工藝廠簽合同的。經過精心篩選后(更多情況下是沒得選),確定你想使用的工藝。在本次實驗中,我使用的是實驗室學長改良過的元件庫,以及TSMC0.18um工藝,EDA工具為CadenceIC614。 7、經過一系列配置之后,“八位格雷碼計數器”已經成為了一個龐大的工程文件,我建議采用TCL腳本文件進行配置。然后就可以進行RTL級綜合。所謂RTL級綜合,實際上是指將Verilog代碼“改寫”為綜合工具(我使用的是Encounter)所能識別的Verilog代碼。通俗的講,這個類似于將“文言文”翻譯為“白話文”,也類似于C語言中的“編譯”,即將高級語言翻譯為匯編代碼。當然,理論上可以直接寫出RTL級代碼,但這就和直接寫匯編語言一樣,復雜程度不言而喻。 8、RTL級綜合完成后,接下來將RTLVerilog導入Encounter進行真正的后端綜合。導入RTL代碼后,還需要說明標準單元庫的LEF文件,并定義電源和地的線名。此時需要一個MMMCconfig配置,流程繁雜,主要是配置相關文件和器件狀態(TT、SS、FF等)。 9、完成導入配置,接下來是芯片布局設計,即Floorplan。Floorplan需要設置一些基礎參數,如芯片的長寬(面積),留給管腳的空間,芯片利用率等。長寬比建議為0.2-5,復雜電路利用率0.85,一般電路利用率0.90,簡單電路利用率0.95。 10、POWER計算,以此為根據布置電源線路,主要為ring和stripe。例如,某數字電路芯片功耗為55mW,增加冗余量到2倍左右,設計為100mW,按照1.8V供電,電流約為60mA,也就是總電源線為60u,如果每條線10u,則六條電源線,兩側各一條,中間四條。Encounter中有專門的布線配置器。布線之后,可以先Apply,然后撤銷反復嘗試。 11、布置IO管腳。如果提前沒有導入IO,可以重新導入(TCL),也可以自行調整。 12、Pre-Place,因為Verilog中往往有很多的module,每個module對應一個布局模塊,布局時應當注意一些布局原則。布局時一般通過簡單的拖動就可以。“八位格雷碼計數器”因為只有一個module,因此不需要復雜的布局。 13、布局是一個不斷修改和改進的過程,Pre-Place之后進行Place,之后進行之后Post-Place。Place之后,需要進行時鐘樹綜合(CTS),時鐘樹綜合的目的是為了讓每個信號都在約束的時間內傳輸到下一個時序單元,否則會對芯片的主頻產生影響(主頻是在設計前就定下來的指標),然后在Post-CTS對不符合時鐘約束的部分進行布線調整。 14、布局之后進行布線,即Route,對于特殊還布線需要進行SRoute,然后進行Post-Place,這些步驟某種程度上都是“點按鈕”和“配參數”,但后端綜合時一定要有清醒的頭腦,必須知道為什么要點這些按鈕,以及該配置什么參數。 15、布局布線經過多次迭代,IO管腳配置好后,可以Fill全圖,用各層金屬覆蓋未使用的區域。單個“八位格雷碼計數器”因為結構簡單,芯片未覆蓋區域較大。 16、至此,Encounter內的后端綜合就完成了,可以導出(export)成GDSII格式的網表,以及為了做DRC,LVS檢查,也需要“Netlist”成schematic(電路原理圖)的格式。 17,將后端綜合的GDSII文件導入(Streamin)到Virtuoso里。Virtuoso是一個用于模擬集成電路設計的軟件。將GDSII文件導入該軟件主要有兩個目的,一是可以在Virtuoso里做“后仿真”,驗證經過后端綜合的一系列流程之后,概念芯片是否能滿足設計需求,此時的仿真就已經考慮到了延時,電阻,功耗等實際存在的問題,如果仿真時出現了問題,需要進行返工修改,必要時要重新布局布線。當“后仿真”通過后,還要對該芯片進行DRC和LVS檢查,DRC是查看是否滿足所選工藝的要求,因為在實際情況下,一些理論上的值是不現實的,比如過細的線無法生產,柵極間的距離過短可能會導致短路,導線和各金屬層之間的電容會影響電路功能等。LVS是比較layout和Schematic之間的拓撲關系是否不一致。二是可以方便以后做數模混合芯片設計時進行混合設計,因為模擬集成電路的是直接在Virtuoso中進行的,兩者最后結合在一起,就可以進行數模混合集成電路設計。 18、進行完檢查之后,就可以與工藝提供廠家聯系進行加工了,如TSMC。一般加工需要跟上企業的業務流程。大約經過1月左右,芯片加工完成,然后進入測試環節。焊接,試驗,驗證芯片指標,以及提出改進方案。 至此,一個數字集成電路從概念到實物的整個流程就完成了,每一步都值得研究和回味,從二四譯碼器到復雜的CPU,其流程是基本一樣的。經過研一上一個學期的學習,我也基本掌握了這個流程。以后會更加努力的在本專業方向繼續前進,培養核心競爭力。

如何規劃好PCB設計布線層數

先看層數規劃的要點

1、信號層數的規劃;

2、電源、地層數的規劃。

一、信號層數規劃方法

要規劃好信號層的層數,主要是計算好各個主要部分

的布線通道。

那么具體的方法有幾點?讓我們為了一起來看看,為了Money前進吧!

1、首先評估主要IC部分的出線通道,比如針對有BGA

器件的設計項目,考慮BGA的深度和BGA的PIN間距,去

規劃出線層數,一般1.0mm焊盤間距及1.0mm以上間距

的,一般過孔間可以過2根線,0.8mm焊盤間距及以下的一

般BGA過孔間只能過一根線。比如有連接器,需要考慮連

接器的深度,需要考慮其2個管腳間的過線數來評估出線

層數。

2、評估好板子上的高速信號布線通道,一般PCB設計

時,高速信號線寬線距有嚴格的要求,限制條件較多,要

考慮跨分割、STUB線長度、線間距等內容,計算好高速

信號區域需要的通道數和需要的布線層數。

3、評估瓶頸區域布線通道,在基本布局處理好之后,

對于比較狹窄的瓶頸區域需要重點關注。綜合考慮差分

線、敏感信號線、特殊信號拓撲等情況來具體計算瓶頸區

域最多能出多少線,多少層才能讓需要的所有線通過這個

區域。

二、電源、地層數的規劃

電源的層數主要由電源的種類數目、分布情況、載流

能力、單板的性能指標以及單板的成本決定。電源平面層

數評估一般考慮電源互不交錯、相鄰層重要信號不跨分

割。

地的層數設置則需要注意以下幾點:主要器件面對應

的第二層要有比較完整的地平面;高速、高頻、時鐘等重

要信號要參考地平面;主要電源和地平面緊耦合,降低電

源平面阻抗等等。

人們經常說:學理走天下呢,你們還得感謝我們為這個國家帶來的建設呢!累了就吃吃東西獎勵這么努力的自己,還是不能虧待自己滴~

綜合考慮了信號層數以及電源、地層數的兩點,基本上不會出現有部分線走不通,臨時加層,然后大規模修

改,浪費時間成本的情況發生。

數碼管時鐘如何添加無線WiFi模塊

要給數碼管時鐘添加無線WiFi模塊,首先要購買一款適用的無線WiFi模塊,如ESP8266或ESP32。

接著,需要將模塊連接到數碼管時鐘的電路板上,通過串口通信來控制模塊的WiFi連接和數據傳輸。

然后,在代碼中添加WiFi連接和數據傳輸的代碼,可通過網絡控制數碼管時鐘的時間和功能。需要注意的是,操作時需注意電路的安全性和專業知識。

好了,本文到此結束,如果可以幫助到大家,還望關注本站哦!

渝公網安備 50011302001640號

渝公網安備 50011302001640號